# Implementation of a 10-bit 5Ms/s Successive Approximation Register Analog-to-Digital Converter.

## (一)背景介紹

在現今數位化發展的時代，對於類比數位轉換器(ADC)在低功耗、小面積以及中等解析度的需求日益增加。逐次漸近式ADC(SAR ADC)因具備電路架構簡單、功耗低及面積小的優點，特別適合應用於這些領域。然而，在中高解析度設計中，SAR ADC的精度與速度往往受到電容陣列匹配度及充放電時間的限制，因此如何在有限資源下達到解析度與速度的平衡，成為值得研究的課題。

## (二)實作方法

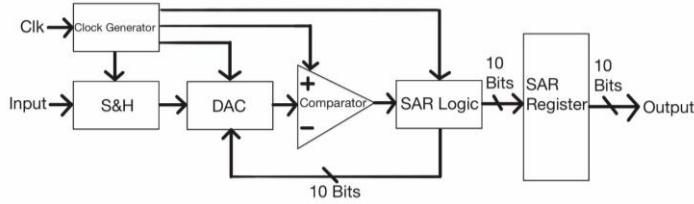

在本次專題中，使用 TSMC T18 製程，製作電源電壓 1V 與取樣頻率 5MS/s 的十位元逐漸逼近式類比數位轉換器，過程包含佈局前模擬，完成電路佈局，通過 DRC、LVS 驗證。整體電路包含時脈產生器(Clock Generator)、靴帶式開關(Bootstrapped Switch)、數位類比轉換器(Digital to Analog Converter, DAC)、動態比較器(Dynamic Comparator)、逐漸逼近式邏輯控制電路(SAR Logic)以及逐漸逼近式暫存器(SAR Register)。

## (三)硬體架構

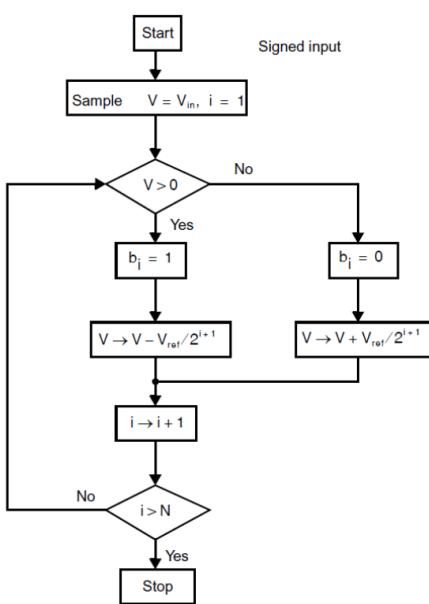

## (四)運作流程圖

## (五)實作成果

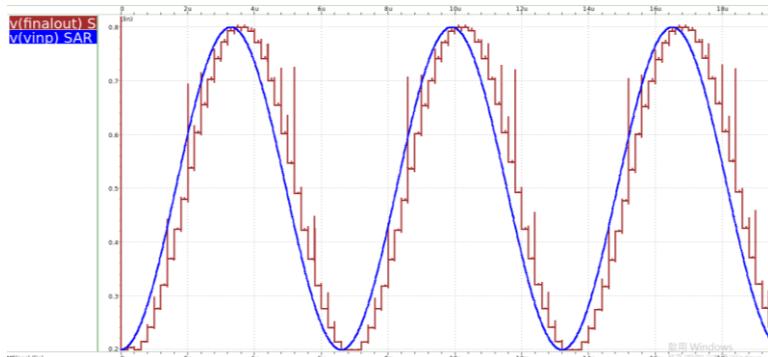

Pre-sim 波形結果

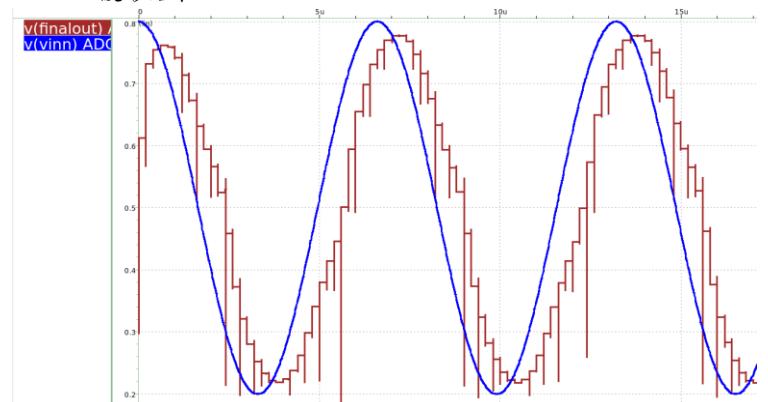

Pro-sim 波形結果

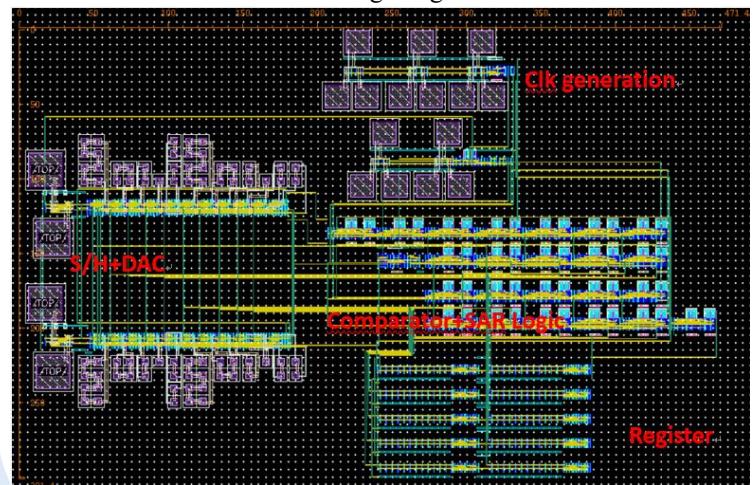

Automatic Placement and Routing integrated circuit

晶片數據:使用 TSMC 0.18um 製程，面積為  $301.4 \times 471.4 \mu\text{m}^2$ 。

## (七)結論

此專題以 TSMC 0.18um 製程實現工作電壓為 1V，取樣頻率 5MS/s 的 10 位元 SAR ADC。在原有的 DAC 電路中，採用分段式結構來降低總電容數，進一步改善穩定時間過長和面積太大的問題，並使用二分搜尋法，根據比較器輸出來決定最後的輸出數值。此外，於 SAR Logic 電路做電容切換策略的邏輯調整，此策略可以維持共模電壓來提高位元轉換的線性度。