# 增益峰值抑制與暫態響應強化的無外部輸出電容線性穩壓器

組別：晶片系統組 專題生：張祖銘 專題指導老師：黃崇勛 教授、葉經緯 教授

## 摘要與背景介紹

隨 SoC 高度整合，外掛大容量輸出電容不利面積與封裝成本。無外部電容的低壓降線性穩壓器（LDO）以內部補償降低對輸出電容 ESR 零點的依賴，需在寬負載、低壓差下抑制複數極點與增益峰化等穩定性問題，並兼顧 PSR、低靜態電流與快速暫態，成為現代片上供電重點議題。又受 PVT 漂移與低電壓化挑戰，設計需平衡穩定度與效率，並確保 Line / Load Regulation 表現。

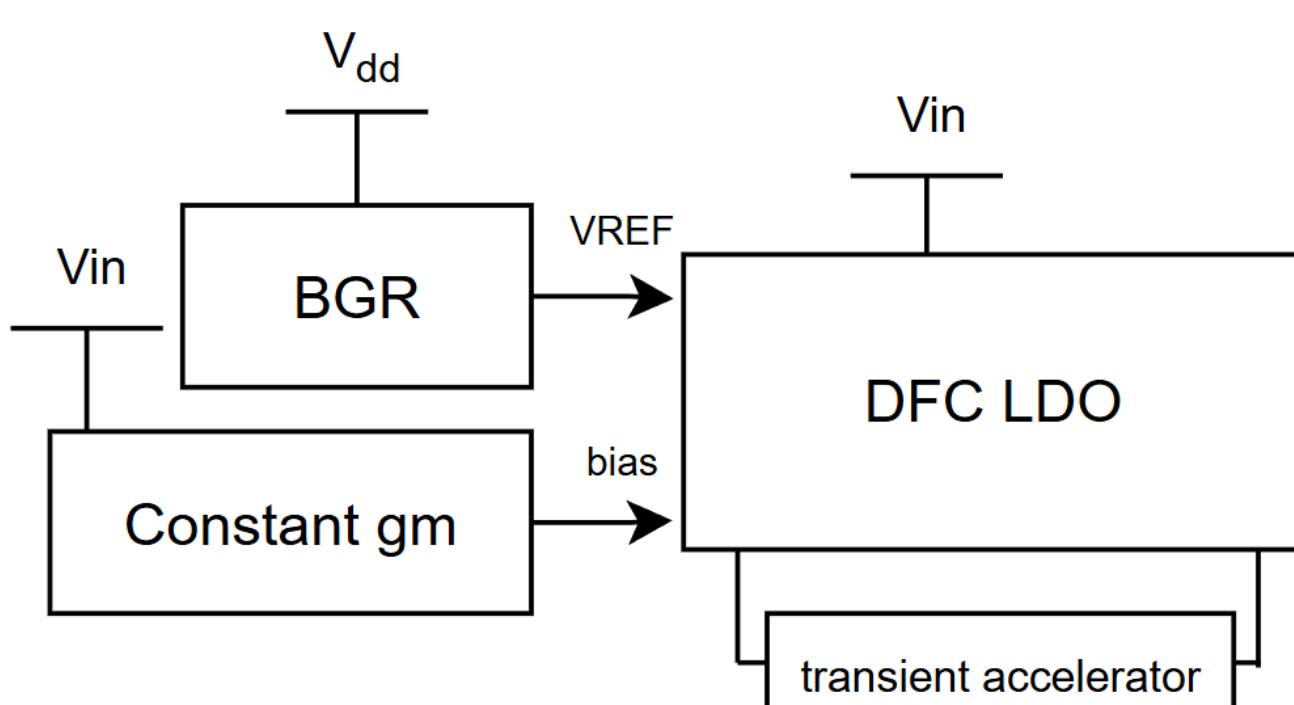

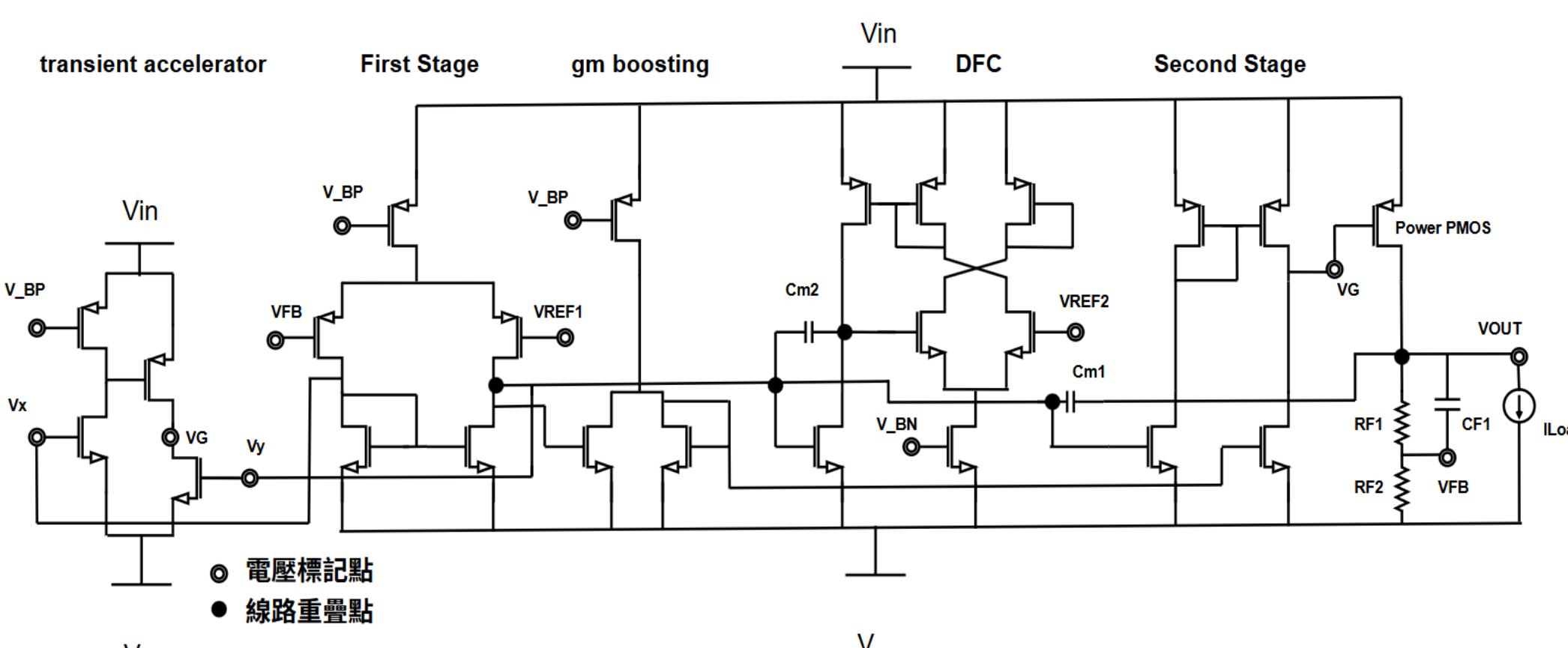

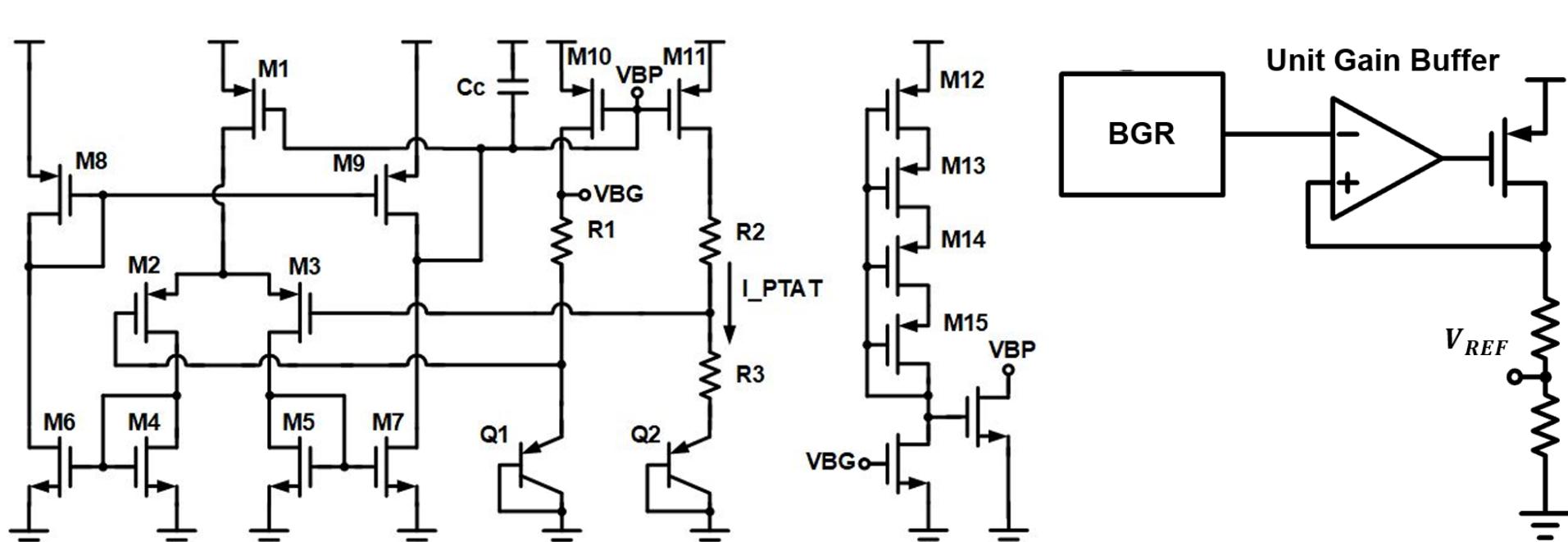

本專題針對低壓 SoC 混訊系統之片上供電，設計一款具增益峰化抑制與暫態強化之低壓降線性穩壓器（LDO）。為解決多能量儲存節點耦合所致的複數共軛極點與相位裕度壓縮問題，本設計採用二級放大合併 gm-boosting，並利用 Damping-Factor-Control 支路以提升阻尼因子，使設計於單位增益交越附近滿足  $\zeta \geq 0.707$  而抑制 gain peaking。偏壓由 constant-gm 產生，參考電壓採 bandgap，以降低 PVT 漂移。為加速大電流躍變之動態回復，另加入 Transient Accelerator，於負載突變時對 Power MOS 之閘極提供瞬時充放電路徑以提前響應。

## 電路架構介紹

本 LDO 架構分為五部分：

- 參考與偏壓：以 bandgap 與 constant-gm 產生穩定  $V_{ref}$  與  $I_{bias}$

- 誤差放大器：二級放大整合 gm-boost 與 Miller 補償

- 阻尼因子控制（DFC）：抑制增益峰化，提升 Phase Margin

- 功率級：P 型 pass 元件受 EA 驅動，輸出經分壓回授

- 暫態加速器（TA）：負載突變時提供閘極快速充放電。

圖一、完整電路之 Block Diagram

圖二、DFC LDO with Transient Accelerator Schematic

圖三、所使用的Bandgap 架構 (a) Bandgap Reference 本身

(b) 外接 buffer 和分壓網路

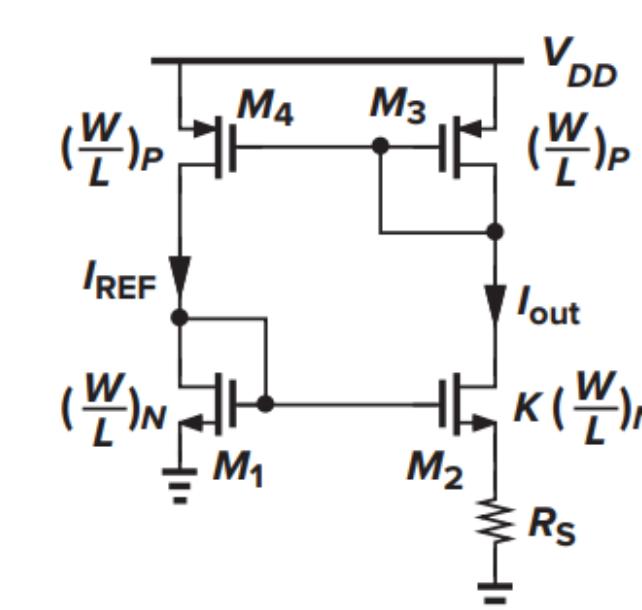

圖四、所使用的 constant-gm

## 模擬與比較

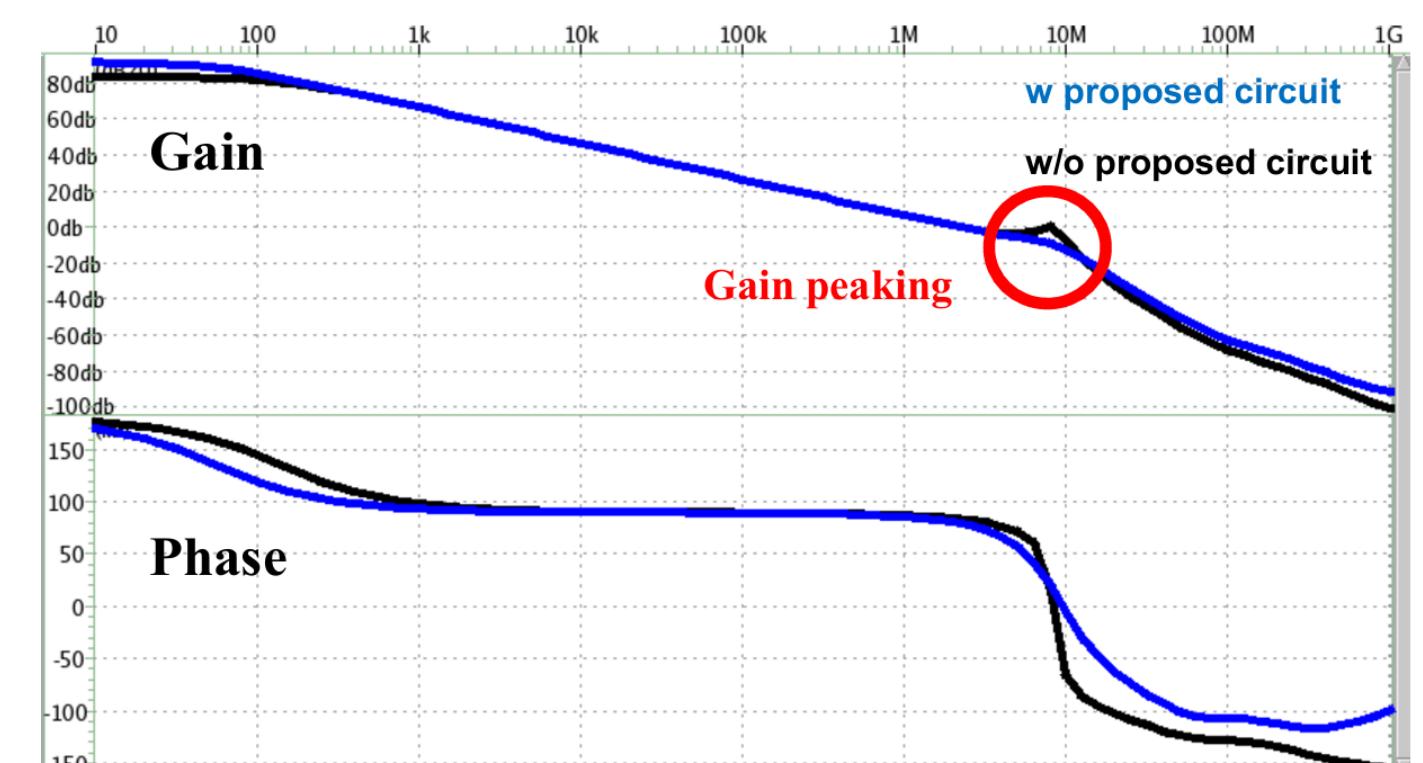

圖五、有無 DFC 和 gm boosting 架構的 Bode plot 比較

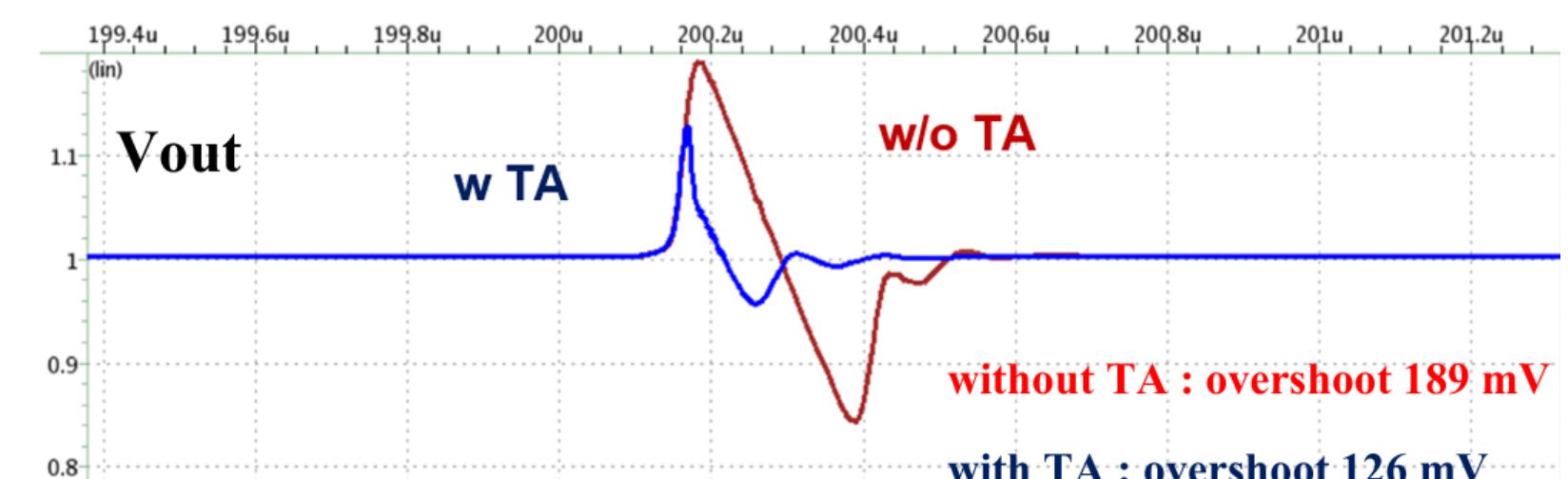

圖六、在重載轉輕載下有無 TA 架構的 Load Transient Overshoot 比較

## 模擬結果

在 MOSFET / BJT / RNHR1000 / MIMCAPS 皆在 Typical Case， $V_{IN} = 1.2\text{ V}$  / Temp = 50 °C 下的模擬結果：

| Specification (under TT 1.2 50)      | Heavy (100mA) | Light (100uA) |

|--------------------------------------|---------------|---------------|

| Process                              | U18           |               |

| VDD (BG)                             | 1.8 V         |               |

| Vin                                  | 1.2 V ~ 1.8 V |               |

| Phase Margin                         | 80.587°       | 86.19°        |

| Gain Bandwidth product               | 1.607 MHz     | 1.85 MHz      |

| Loop Gain                            | 78.1 dB       | 90.54 dB      |

| Power                                | 119.46 mW     | 0.6356 mW     |

| Line Regulation (heavy)              | 0.0045 mV/V   |               |

| Line Regulation overshoot/undershoot | Ov: 56.66 mV  | Un: 48.04 mV  |

| Load Regulation                      | 0.00121 V/A   |               |

| Load Regulation overshoot/undershoot | Ov: 126.53 mV | Un: 533.17 mV |

| PSR (@1k Hz)                         | -48.52 dB     | -48.69 dB     |

| PSR (@10k Hz)                        | -35.03 dB     | -35.07 dB     |

| PSR (@100k Hz)                       | -15.67 dB     | -15.7 dB      |

| vout                                 | 1.0023 V      | 1.0024 V      |

## 結論與參考文獻

本專題實現具 DFC 與 TA 之 LDO：DFC 提升阻尼、抑制交越附近增益峰化；TA 以閘極快速充放電強化暫態，將 Load transient overshoot 由 189 mV 降至 126 mV。而蒙地卡羅模擬結果顯示相位裕度最差情況下重載 55° / 輕載 64°， $V_{out}$  維持  $1\text{ V} \pm 7\%$ 。

Reference:

[1] C. -H. Huang, Y. -T. Ma and W. -C. Liao, "Design of a Low-Voltage Low-Dropout Regulator," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 22, no. 6, pp. 1308-1313, June 2014

[2] Ka Nang Leung and P. K. T. Mok, "A capacitor-free CMOS low-dropout regulator with damping-factor-control frequency compensation," in *IEEE Journal of Solid-State Circuits*, vol. 38, no. 10, pp. 1691-1702, Oct. 2003