## 摘要

現今多數高速無線通訊標準皆採用低密度同位檢測碼 (LDPC codes) 作為通道編碼方案。LDPC codes 不僅具備優異的錯誤更正能力，其稀疏結構亦極適合進行硬體平行化處理。本專題針對 Wi-Fi 6 標準進行探討並設計一套具部分平行處理能力的解碼器，採用正規化最小和演算法 (NMSA) 並設定正規化係數  $\alpha = 0.75$ ，使其能透過移位和加法實現。解碼器架構中引入檢測節點功能單元 (CNFU) 與變數節點功能單元 (VNFU) 模組，並結合 efficient chunk 儲存策略，壓縮節點間傳遞之外部訊息所需的資源使用。為提升迭代速度與解碼效率，實作 Simplifier 模組加速運算，此外也引入流水線 (pipeline) 進一步降低關鍵路徑延遲與邏輯資源耗用。針對平行處理架構常見的記憶體存取衝突問題，亦設計排程 (Scheduling) 機制，避免寫入衝突，有效提升吞吐量。最終實現之解碼器，FPGA 於時脈頻率為 108.108 MHz 下可達吞吐量 203.65 Mb/s。

## LDPC code 編碼系統

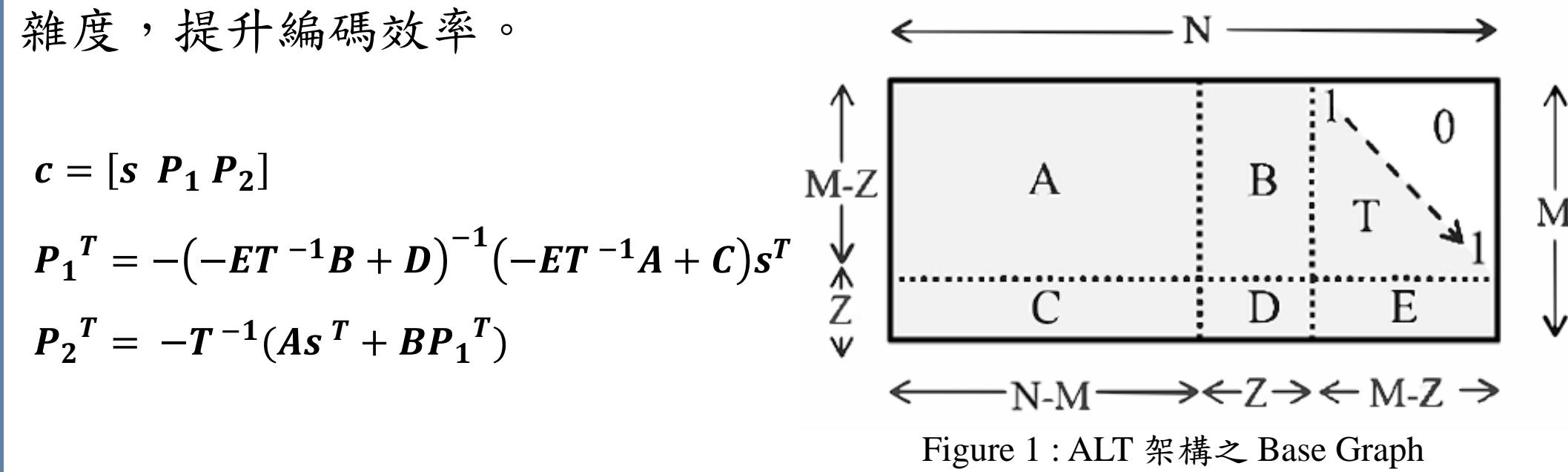

Wi-Fi 6 標準採用 QC-LDPC 碼（準循環低密度奇偶檢查碼），可以通過 Parity-Check Matrix 之 ALT 架構的特性進行快速編碼，降低複雜度，提升編碼效率。

## NMSA 解碼算法

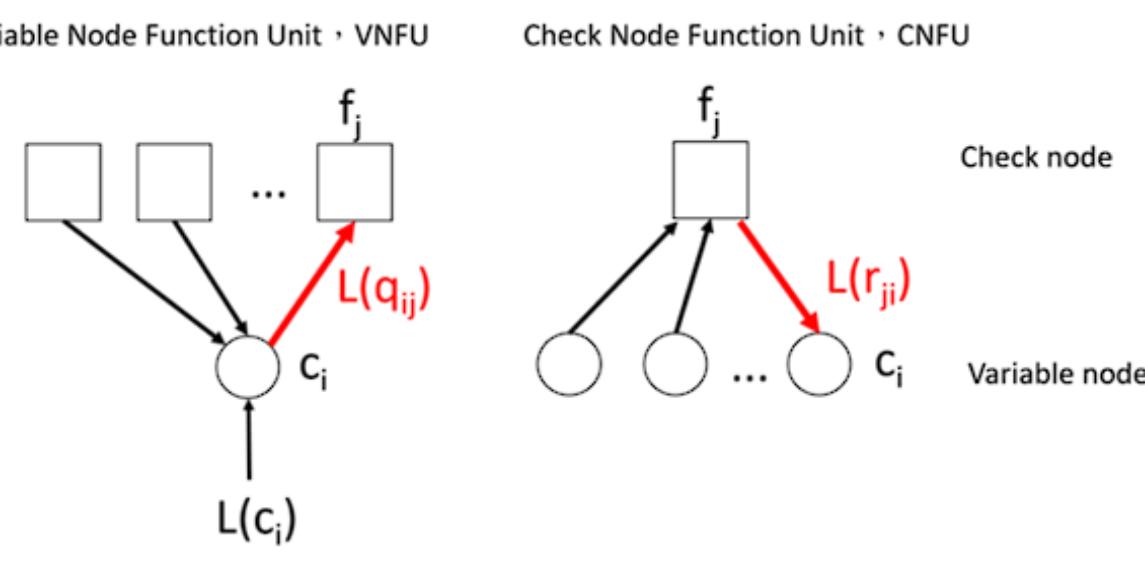

LDPC codes 之解碼演算法採用消息傳遞演算法 (MPA)

Figure 2 : 一次迭代運算操作示意圖

Step 1: 計算後驗機率

Step 2: 更新 Check-to-variable message

$$L(r_{ji}) = \left( \prod_{i' \in V \setminus i} \alpha_{i'j} \right) \times \alpha \times \min_{i' \in V \setminus i} \beta_{i'j}$$

$$\alpha_{ij} = \text{sign}[L(q_{ij})] \quad \beta_{ij} = |L(q_{ij})|$$

Step3: 更新 Variable-to-check message

$$L(q_{ij}) = L(v_i) + \sum_{j' \in C_{i,j}} L(r_{j'i})$$

Step3: 完成一次迭代，硬解碼判斷碼字

$$L(Q_i) = L(v_i) + \sum_{j' \in C_i} L(r_{j'i})$$

$$c_i = \begin{cases} 1 & \text{if } L(Q_i) < 0 \\ 0 & \text{else} \end{cases}$$

## 解碼器流程

在傳統解碼器設計中，如 Figure 3，Check-to-variable message 需等待 Variable-to-Check message 完成後方能更新，運算效能較差。

Figure 3 : 傳統解碼排程

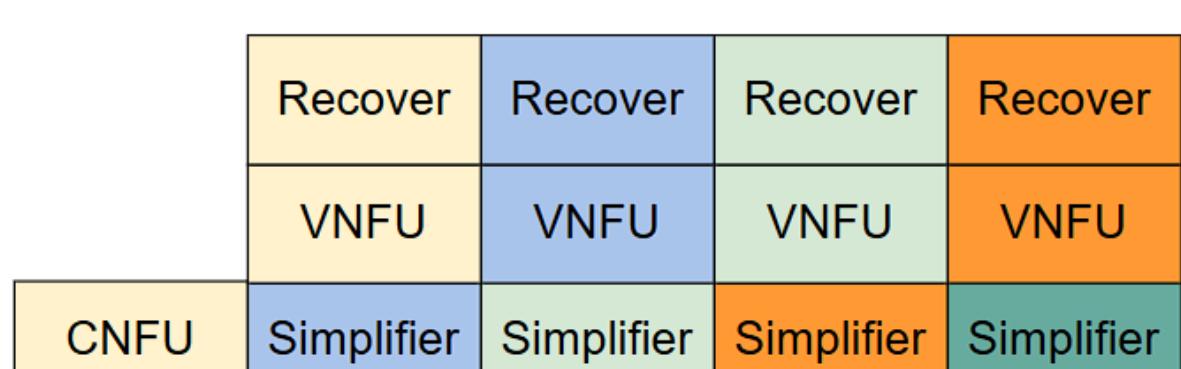

本專題引入 Simplifier，得以在計算 Variable-to-check message 過程中同步更新 Check-to-variable message，從而實現高效解碼運算。

Figure 4 : 引入 Simplifier 設計的解碼排程

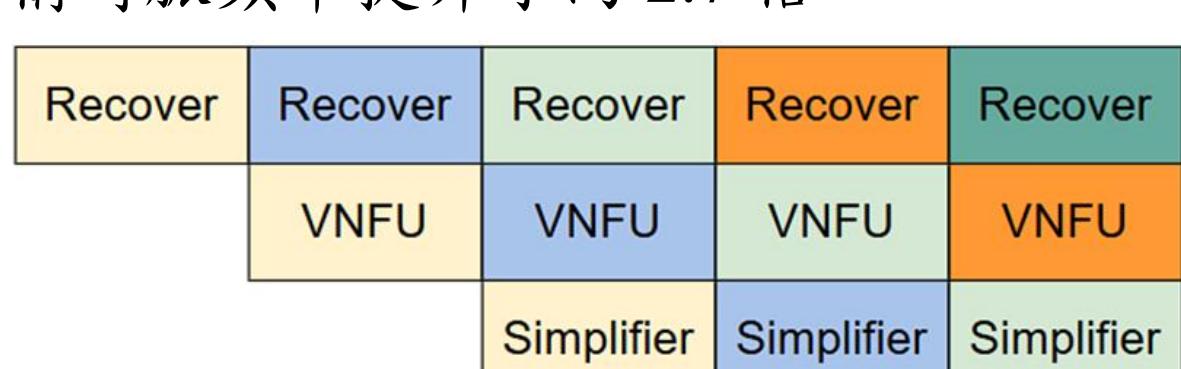

此外，本專題同時引入 pipeline，成功縮短 critical path，相比未使用 pipeline 之架構時脈頻率提升了約 2.7 倍。

Figure 5 : pipeline 解碼排程

## 平行處理之排程

在計算 Variable-to-check message 時，由於 Column by Column 的解碼流程，針對每一行設定了不同的偏移值，使解碼過程得以錯開寫入同個位置之記憶體的時間點，避免記憶體衝突的情形。詳細偏移值如 Table 1。

| VNFU | 1~4行 | 5~8行 | 9~12行 | 13~16行 | 17~20行 | 21~24行 |

|------|------|------|-------|--------|--------|--------|

|      | 2    | 19   | 8     | 18     | 12     | 6      |

|      | 9    | 10   | 6     | 0      | 0      | 2      |

|      | 14   | 12   | 0     | 4      | 20     | 8      |

|      | 8    | 15   | 4     | 2      | 9      | 15     |

Table 1 : VNFU 偏移值設定表

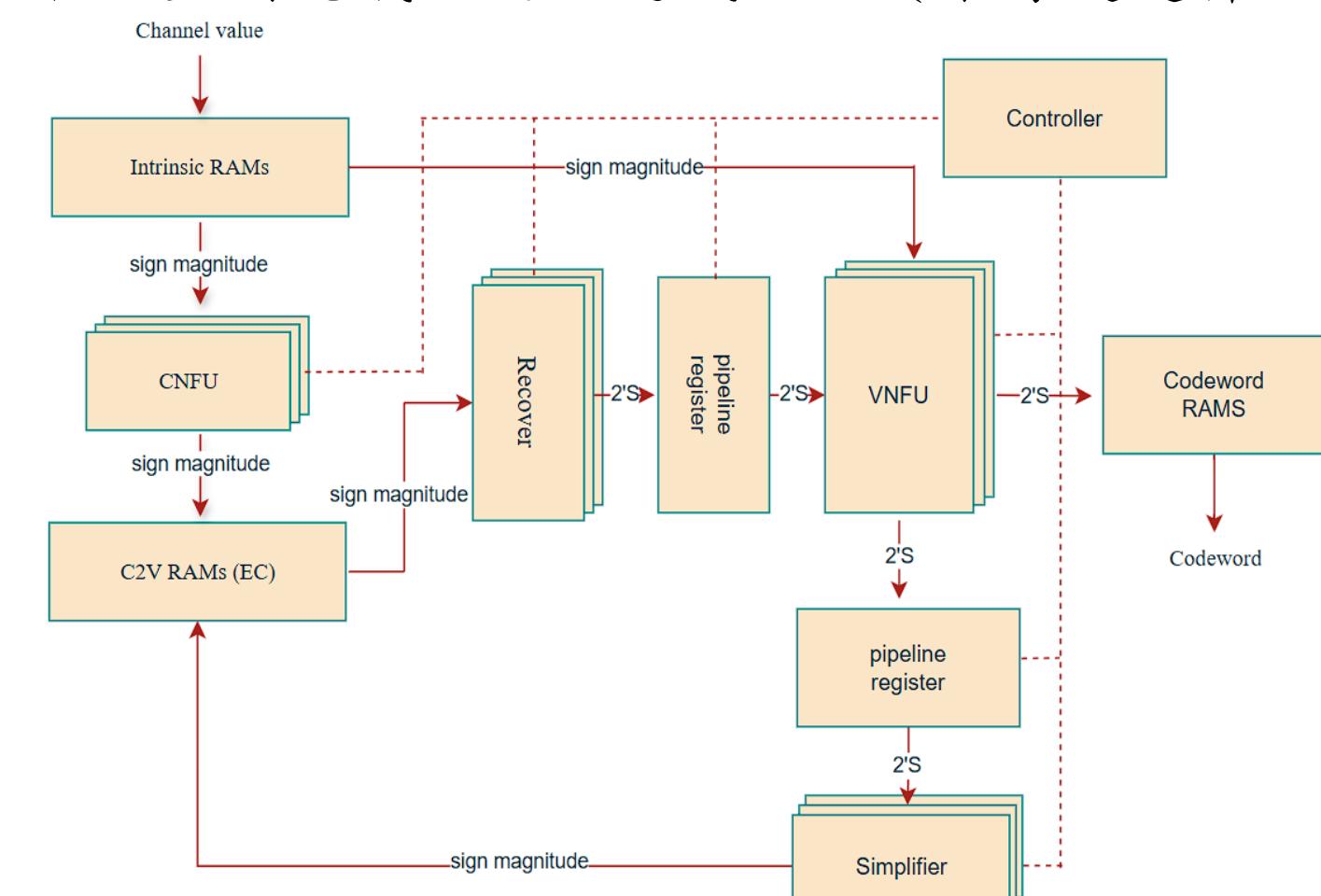

## 解碼器硬體架構

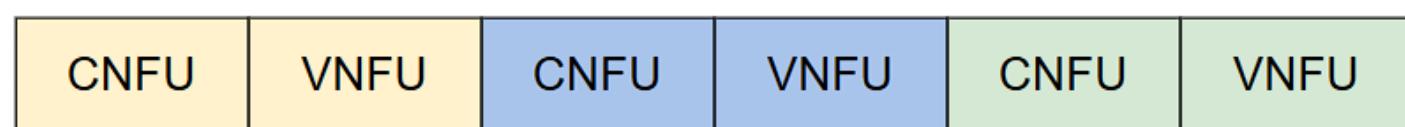

在解碼器中加入平行處理設計，使多個硬體單元同時運算，提升其性能表現。詳細硬體運作過程如下：

1. 接收通道輸入的 LLR messages 並寫入 Intrinsic RAMs。

2. CNFU 透過 LLR messages 計算 Check-to-variable message，並把結果存入 C2V RAMs。

3. 開始循環迭代解碼，Recover 還原 C2V RAMs 中的數據並交由 VNFU 計算 Variable-to-check message，最後將結果交由 Simplifier 更新 C2V RAMs 作為下一次迭代使用。

4. 重複步驟 3. 直到完成設定之迭代次數（本專題選擇 10 次）。

Figure 6 : pipeline 部分平行解碼器總架構圖

## 實作驗證與效能分析

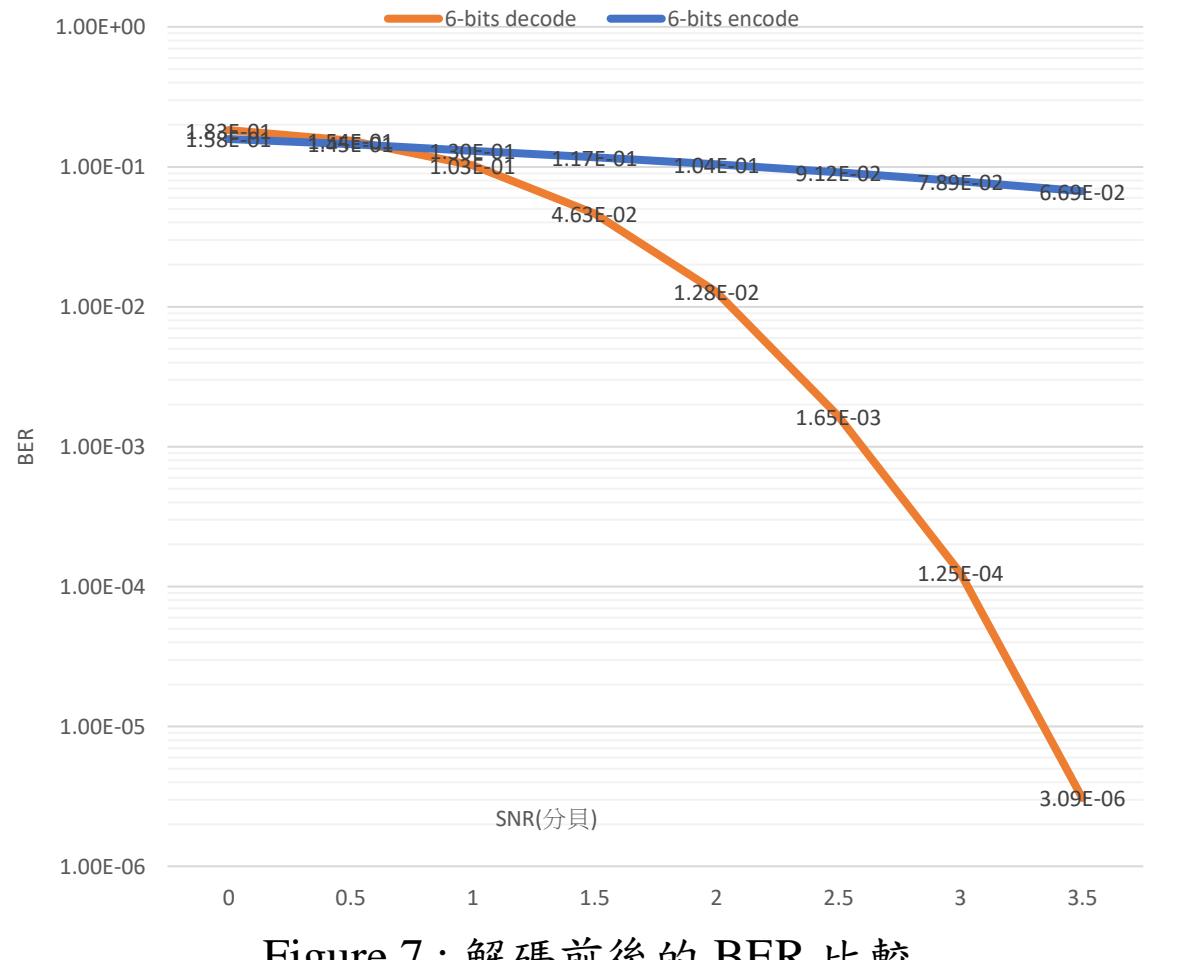

使用 Xilinx Artix-7 FPGA，型號 xc7a200tsbg484-1 進行實作，硬體資源利用率如 Table 2。最終成果在迭代 10 次的條件下，時脈頻率為 108.108 MHz ( $P_{clk} = 9.25 \text{ ns}$ ) 的狀態下，吞吐量為 203.65 Mb/s。分析經解碼後的碼字可得解碼器在 SNR 大於 3.5 dB 時，擁有最佳解碼效能。

| Resource  | Utilization | Available | Utilization (%) |

|-----------|-------------|-----------|-----------------|

| LUTs      | 16598       | 133800    | 12.41%          |

| FFs       | 15894       | 267600    | 5.94%           |

| 36k BRAMs | 1           | 365       | 0.27%           |

Table 2 : 硬體資源使用表

Figure 7 : 解碼前後的 BER 比較

- [1] 陳建宇, IEEE 802.11ac LDPC Codes 高效能解碼器之設計與實作, 國立中正大學通訊工程研究所碩士論文, July 2012.

[2] Y. H. Chen, Jue Hsuan Hsiao and Zong Yi Xiao, "Wi-Fi LDPC encoder with approximate lower triangular diverse implementation and verification," 2014 IEEE 11th International Multi-Conference on Systems, Signals & Devices (SSD14), 2014, pp. 1-6.

[3] 翁偉哲, 適用於 IEEE 802.11ax 的 LDPC Codes 說解碼器研究與實作, 國立中正大學通訊工程學系專題研究報告, June 2024.

[4] IEEE Std 802.11ax-2021, "IEEE Standard for Information Technology—Telecommunications and Information Exchange between Systems—Local and Metropolitan Area Networks—Specific Requirements—Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications—Amendment 1: Enhancements for High-Efficiency WLAN," IEEE, Feb. 9, 2021.

[5] 王定嵐, 張研勤, 適用於低軌道衛星通訊的 LDPC Codes 平行處理解碼器實作, 國立中正大學通訊工程學系專題研究報告, August, 2024.

[6] A. Hasan, L. Lopaciński, G. Panic and R. Kraemer, "High-Throughput Multi-Frame Decoding of QC-LDPC Codes with Modified Rejection-Based Minimum Finding," IEEE Access, vol. 10, pp. 5378-5389, 2022.