# 十位元每秒取樣一千萬次 逐漸逼近式類比數位轉換器之實現

組別：電磁晶片組

專題生：胡志誠

指導教授：吳建華教授

## 摘要

本專題聚焦於實現工作電壓為1V，取樣頻率10MS/s的10位元連續漸進式類比數位轉換器，使用的製程為TSMC T18 CMOS。SAR ADC 架構因在中等解析度、速度和低功耗之間取得了出色的平衡，已成為低功耗應用的首選。簡單的二進位搜尋演算法和較少的類比電路，使功耗顯著降低。這種高效能低功耗特性使其在需要大量 ADC 的系統中極具優勢。

## 電路架構

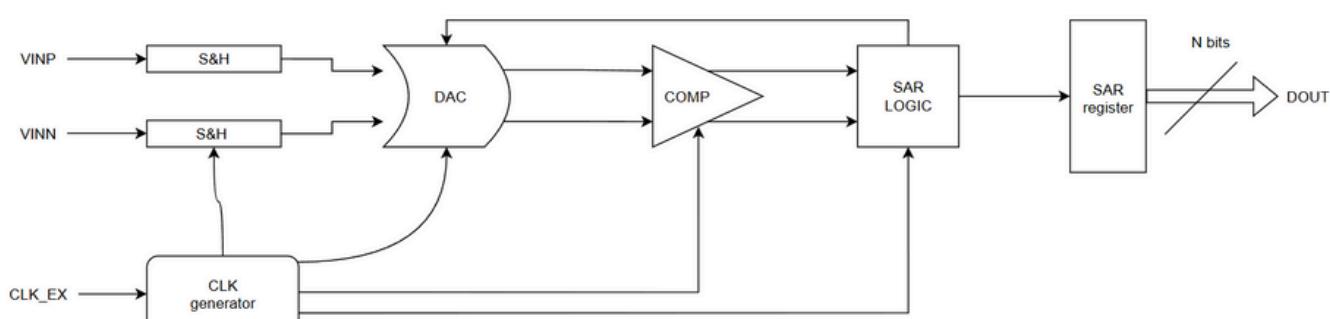

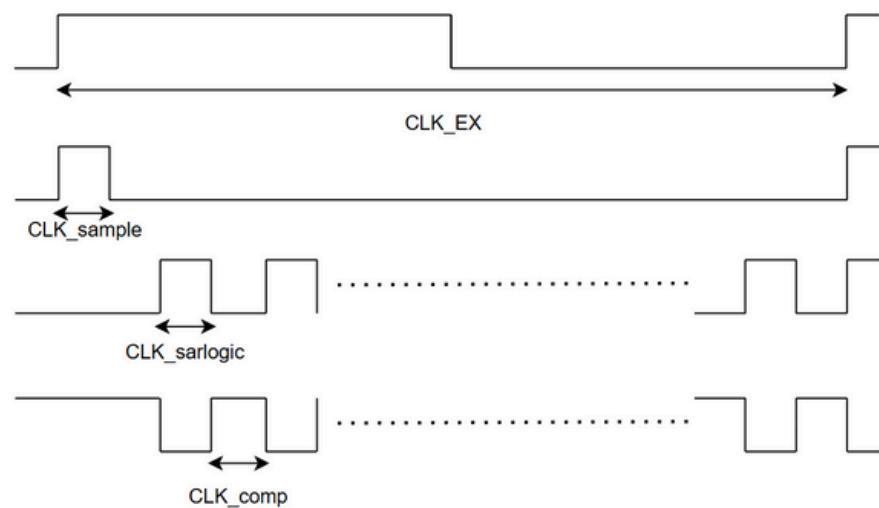

主要由取樣保持電路、數位類比轉換器、比較器、逐漸逼近式邏輯和輸出暫存器組成。如果時脈是由外部提供，雖然邏輯穩定且不易出錯，但無法在ADC內部進行動態調整導致運作速度較慢，且引入過程中可能會有雜訊的產生而出現錯誤。因此單獨設計一個時脈產生器以提高整體的運作效率。

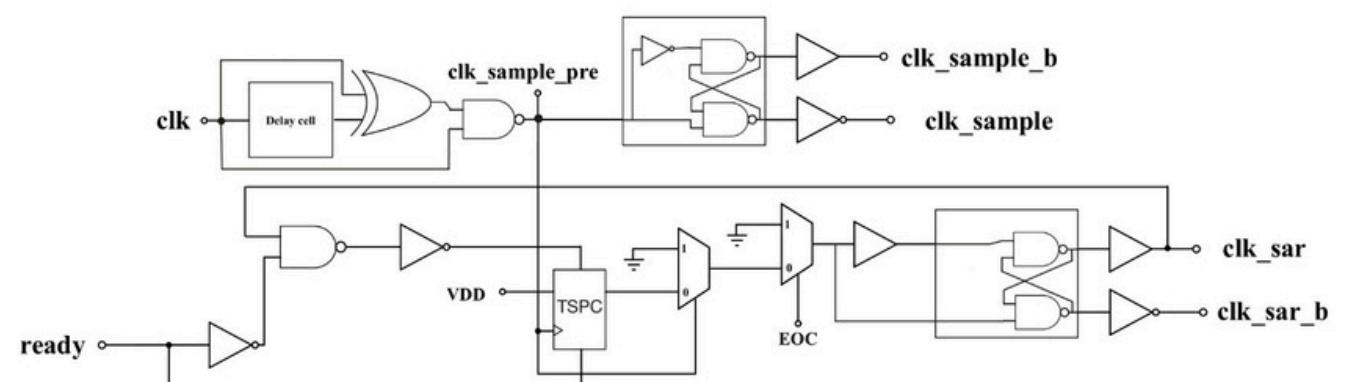

## 時脈產生器

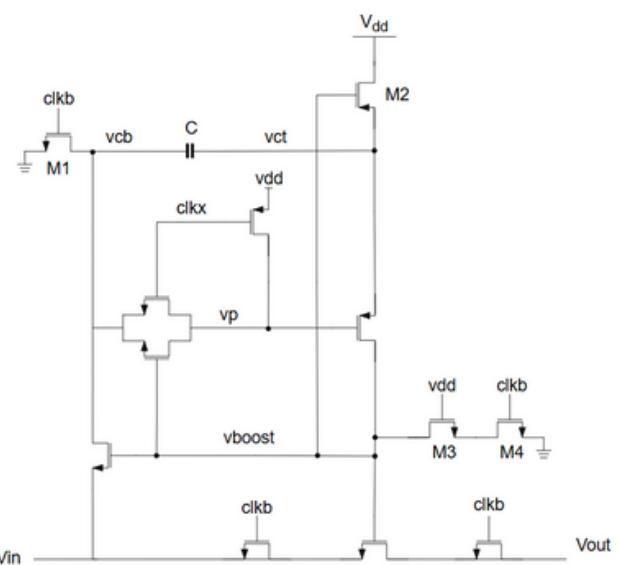

## 取樣電路

採用自舉式電容的靴帶式開關作為取樣電路，由於有自舉電容的電荷保持，即使源極電壓在取樣過程中發生變化，閘極電壓也能通過電容維持電壓於 $V_{in}+V_{DD}$ 。

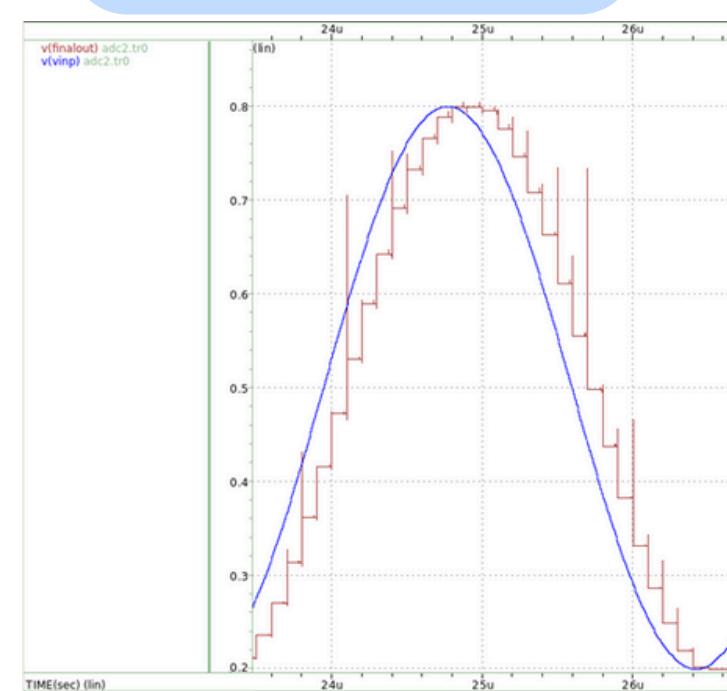

## 模擬數據

|           | Pre-sim | Post-sim |

|-----------|---------|----------|

| corner    | T/T     |          |

| 溫度(°C)    | 27      |          |

| THD(dB)   | -56.22  | -52.52   |

| SNR(dB)   | 62.32   | 56.63    |

| SNDR(dB)  | 55.81   | 51.18    |

| ENOB(bit) | 8.97    | 8.21     |

| SFDR(dB)  | 55.84   | 52.27    |

## 結論

從模擬結果來看，SNDR 下降可能主要是因為電容非理想效應所造成，包括 DAC 電容失配、寄生電容以及通道電荷注入等問題，導致取樣過程出現非線性現象，使總諧波失真增加。為改善這個問題，可以透過電容失配校正技術、優化電容佈局，以及改進開關設計和時序補償電路，降低電壓偏移對 SNDR 的影響。

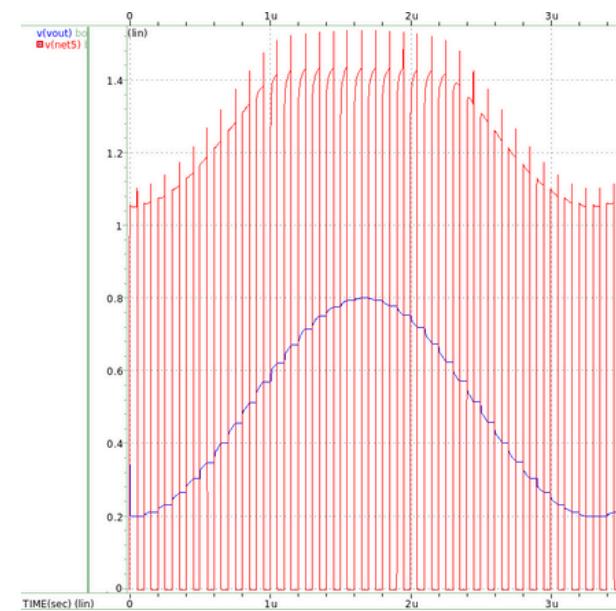

## 模擬波形

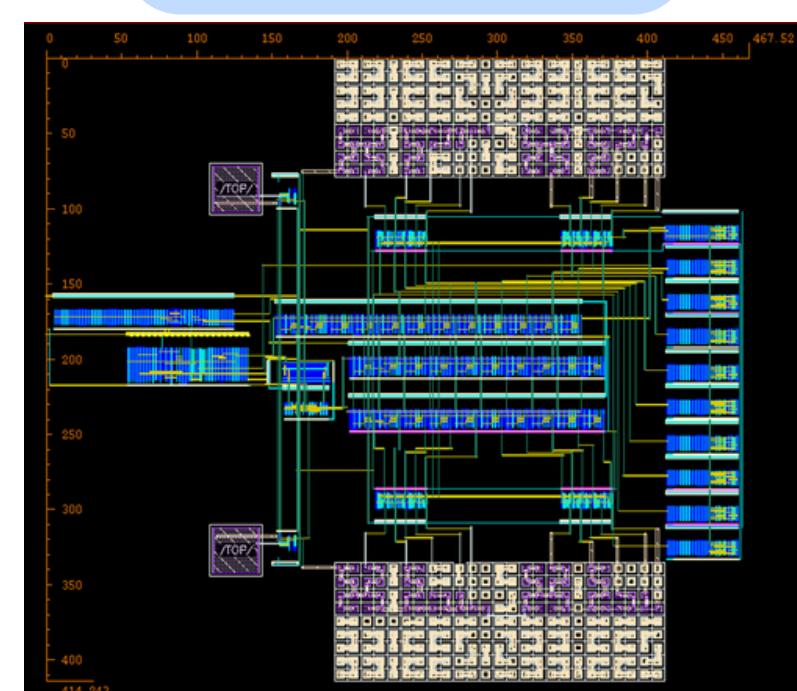

## layout電路

## 相關文獻

- D. Schinkel, E. Mensink, E. Klumperink, E. van Tuijl and B. Nauta, "A Double-Tail Latch-Type Voltage Sense Amplifier with 18ps Setup+Hold Time," IEEE ISSCC Dig. Tech. Papers, June 2007.

D. S. Marathe and U. P. Khot, "A 10-Bit 10-Ms/S 5.72 nW Mixed SAR Logic for ADC Used in Wireless Sensor Node," ICNTE, Jan. 2019.

A. Elkafrawy, J. Anders and M. Ortmanns, "A 10-bit reference free current mode SAR ADC with 58.4 dB SFDR at 50 MS/s in 90 nm CMOS," in Nordic Circuits and Systems Conf. (NORCAS), pp. 1-4, Oct. 2015.