# 使用LC VCO之2.4 GHz整數型鎖相迴路

專題生：陳璕樺、李堂宇、吳昕頤 指導教授：吳建華

## 摘要

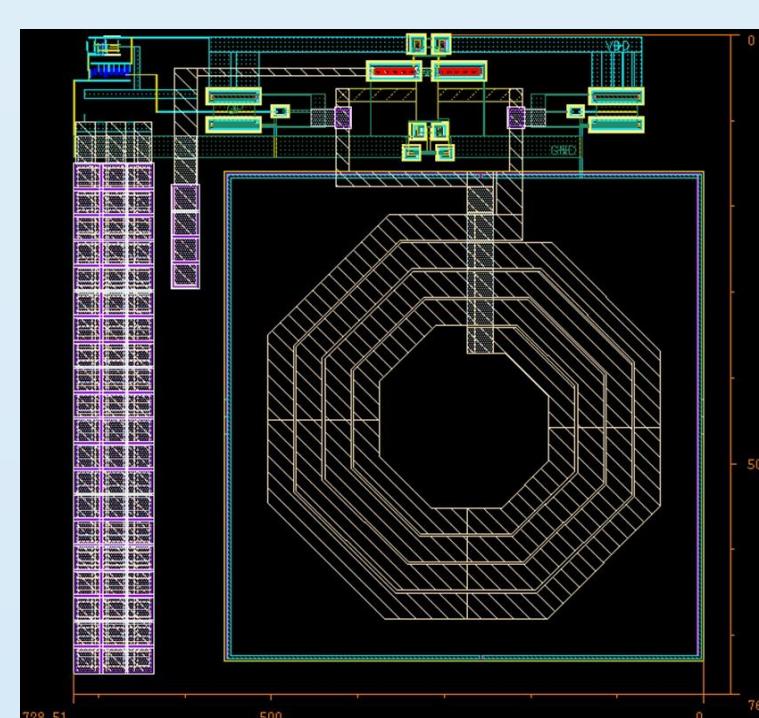

本次專題研究採用 TSMC 0.18- $\mu\text{m}$  CMOS 製程實現以 2.4 GHz 為中心頻率之鎖相迴路 (Phase-Locked Loop, PLL) 設計，其可調頻率範圍為 2.277 GHz ~ 2.543 GHz (11%)，輸入參考頻率為 18.75MHz，除數為 128，電路面積為  $728.51 \mu\text{m} \times 768.79 \mu\text{m}$ ，總功耗約 50.901 mW。系統中各子電路均以 Cadence Virtuoso、HSPICE 與 ADS 進行設計與模擬，並依序完成 Schematic、Pre-layout simulation、Layout 與 Post-layout simulation 之流程。

## 原理

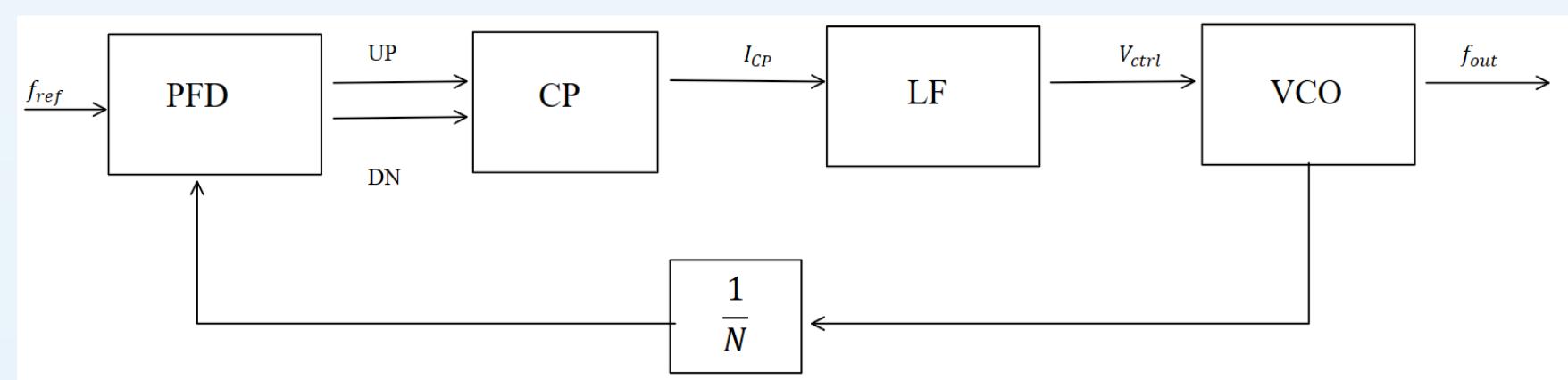

鎖相迴路是一種透過負回授方式來控制整個迴路來產生與輸入參考時脈同步的時脈訊號，如圖 2.1 為一鎖相迴路架構的方塊圖，整個電路架構是由相頻偵測器 (Phase Frequency Detector, PFD)、充電泵 (Charge Pump, CP)、迴路濾波器 (Loop Filter, LF)、壓控震盪器 (Voltage Control Oscillator, VCO)、除頻器 (Divider) 所組成。

↑鎖相迴路系統方塊圖

如圖所示，當一參考訊號  $f_{ref}$  輸入進來後，相頻偵測器會比對參考訊號和回授訊號的相位及頻率差，並輸出對應的 UP 及 DN 訊號供充電泵進行充放電。而迴路濾波器則可以把充電泵輸出的電流訊號  $I_{CP}$  轉為電壓訊號  $V_{ctrl}$ ，再透過這個電壓訊號來控制 VCO 所產生的振盪頻率，最後用除頻器來把輸出的頻率降低並回授給相頻偵測器跟參考訊號做比對。經由這整個過程可將回授訊號與參考訊號的相位和頻率幾乎同步，充電泵與迴路濾波器會輸出一個穩定的電壓，讓 VCO 產生一個穩定的頻率  $f_{out}$ 。此時電路會進入穩態，系統即鎖定。而最後輸出的頻率則會是參考訊號  $f_{ref}$  的  $N$  倍， $N$  為除頻器的除數，可表示為：

$$f_{out} = f_{ref} \times N$$

## 相位頻率偵測器(PFD)

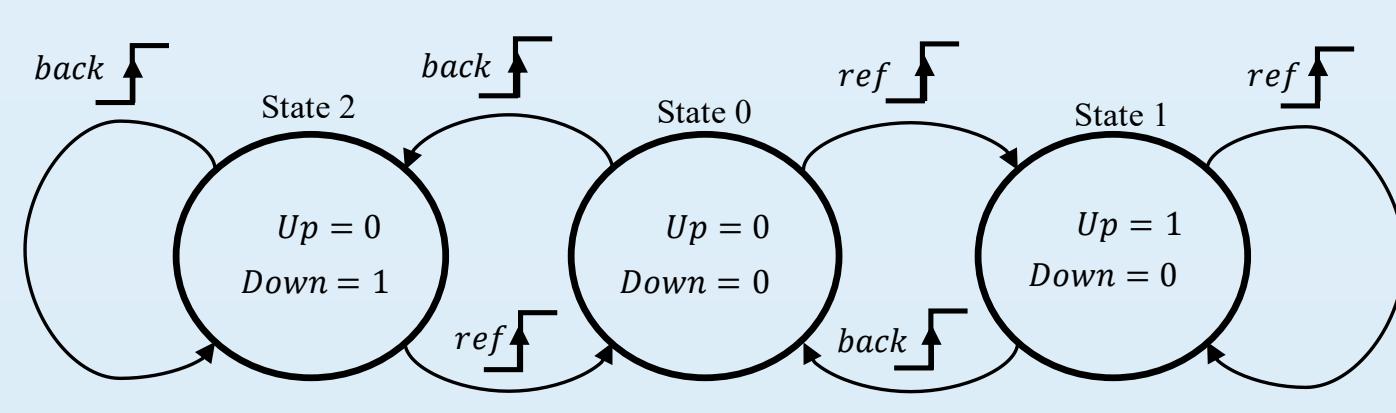

相位頻率偵測器是一種判斷兩個輸入訊號之間的相位差與頻率差，並輸出相應的數位訊號 Up 與 Down 給下一級的充電泵來充放電。圖中 ref 為輸入參考訊號、back 為回授訊號。

↑相位頻率偵測器狀態圖

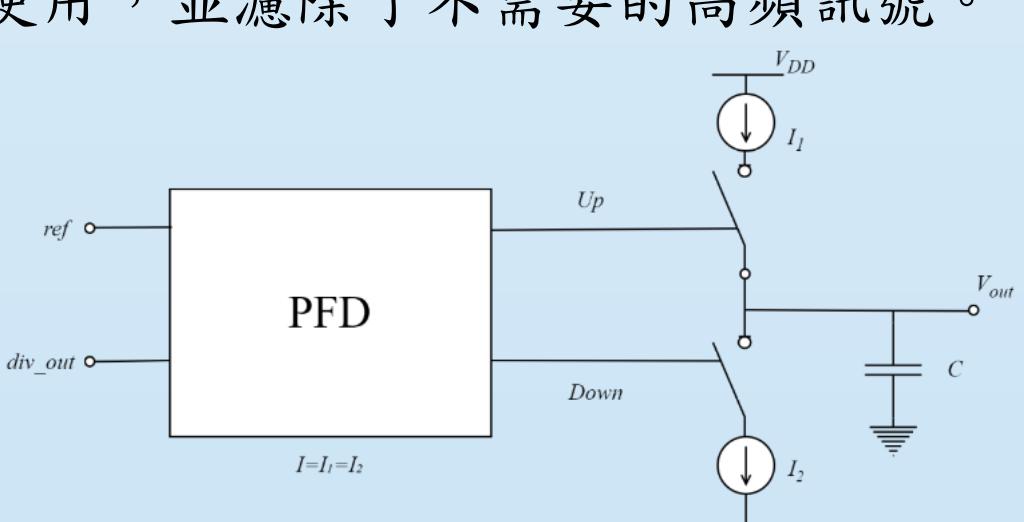

## 充電泵與迴路濾波器(CP & LF)

充電泵的功能就是把相頻偵測器所傳來的輸入訊號相位差，轉換成等比例的電流訊號，而濾波器則是把電流訊號再轉成電壓訊號供下級的壓控震盪器使用，並濾除了不需要的高頻訊號。

↑相位頻率偵測器結合理想充電泵及簡易濾波器的電路示意圖

## 壓控震盪器(VCO)

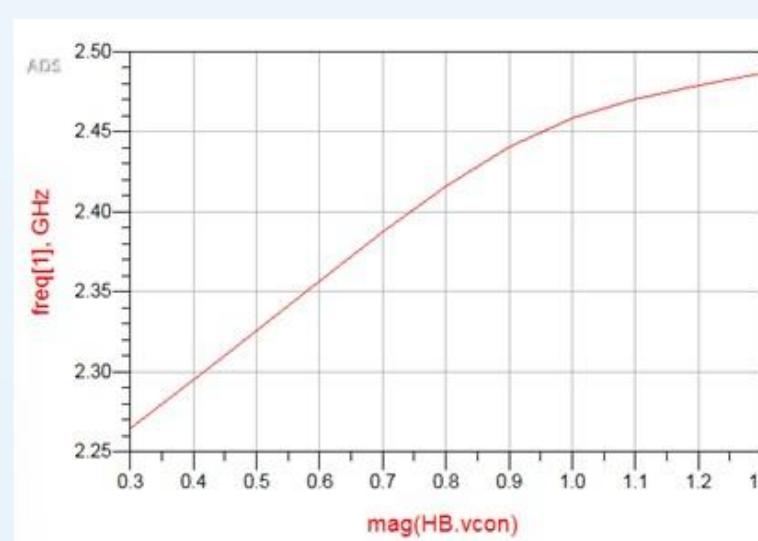

壓控震盪器 (VCO) 是一種透過電壓來產生並控制振盪頻率的電路。藉由前一級的充電泵及迴路濾波器所產生的控制電壓  $V_{ctrl}$ ，來控制鎖相迴路的輸出頻率。

輸出訊號則由電感及可變電容結合的諧振腔來產生一個隨輸入電壓  $V_{ctrl}$  來變動的對應輸出頻率。

↑VCO 調頻範圍

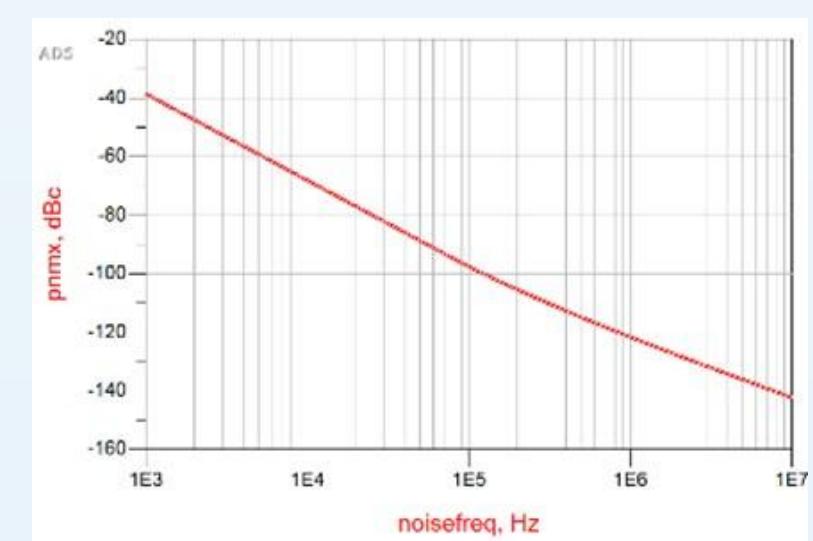

↑Phase noise

## 除頻器(FD)

除頻器主要功能為降頻及整波。本實驗選擇使用 TSPC DFF，可以減少時間延遲、執行相對快速的操作頻率。

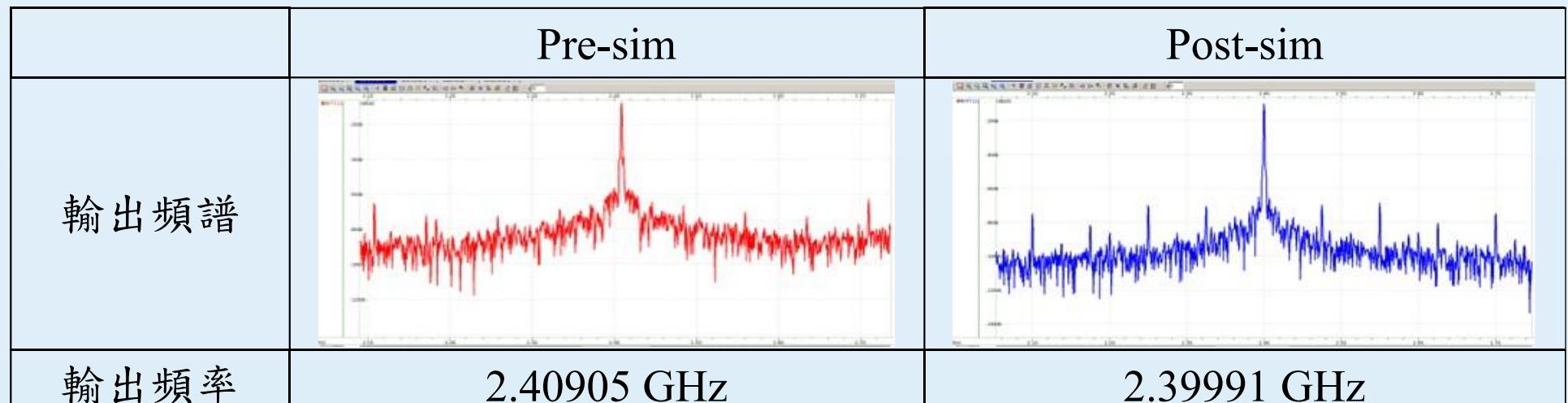

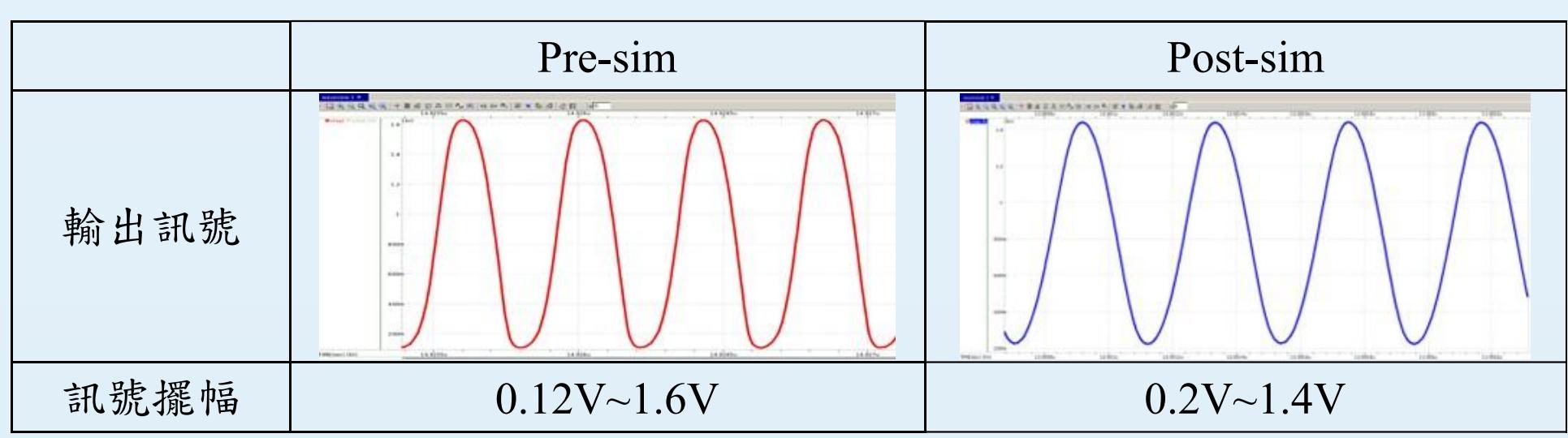

## 模擬結果

↑鎖相迴路系統方塊圖

| Corner | Power supply (V) | Temperature (°C) |

|--------|------------------|------------------|

| TT     | 1.62             | -40~125          |

|        | 1.8              | -40~125          |

|        | 1.98             | -40~125          |

| SS     | 1.62             | 25~125           |

|        | 1.8              | -40~125          |

|        | 1.98             | -40~125          |

| FF     | 1.62             | -40~125          |

|        | 1.8              | -40~125          |

|        | 1.98             | -40~125          |

## 結論

由 PVT 的模擬結果，可看出本實驗可適用於各種環境，僅 SS/1.62V/125°C 無法鎖住，進一步研究有發現其無法鎖住的原因為 VCO 輸出擺幅過低，導致除頻器邏輯準位錯誤，未來會再調整 VCO 後的 buffer 來拉高輸出擺幅。