# 應用於 LTE 4G Band 3 之整數型鎖相迴路

指導教授：吳建華 組員：余冠禎、張傑甯、袁嘉謙

## 摘要

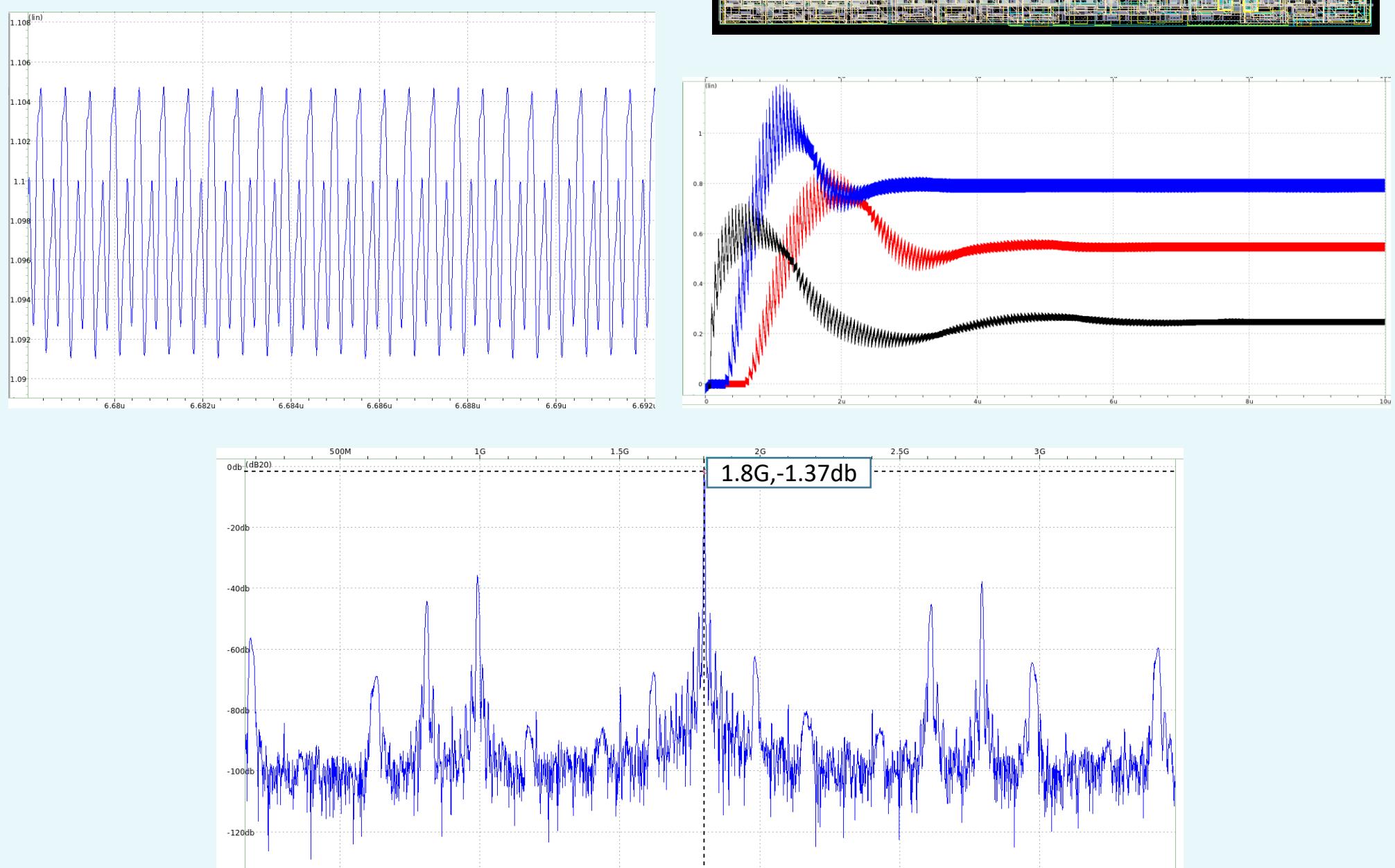

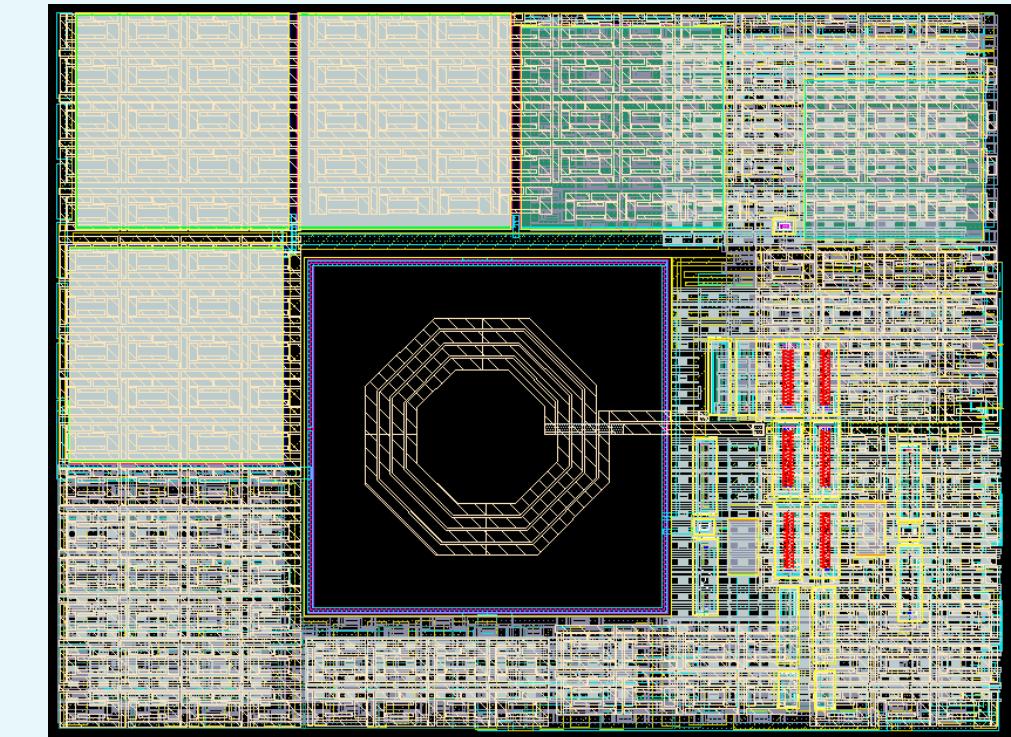

本專題研究針對 LTE 4G Band 3 頻段設計一整數型鎖相迴路，以 TSMC 0.18  $\mu\text{m}$  RF CMOS 製程實現，輸出頻率為 1.8 GHz、參考頻率為 20 MHz。整體架構採用 LC 壓控震盪器，二階迴路濾波器與預充電式相位頻率偵測器，並透過優化充電泵電流匹配與調整迴路參數以提升鎖定精度、降低抖動以增進整體系統穩定度。模擬結果顯示 PLL 在典型製程下鎖定時間約為 5  $\mu\text{s}$ ，輸出頻率達 1.8 GHz，整體功耗約 120 mW，鎖定時電壓抖動約 14 mV，晶片面積為  $578 \times 751 \mu\text{m}^2$ 。

## 基本架構

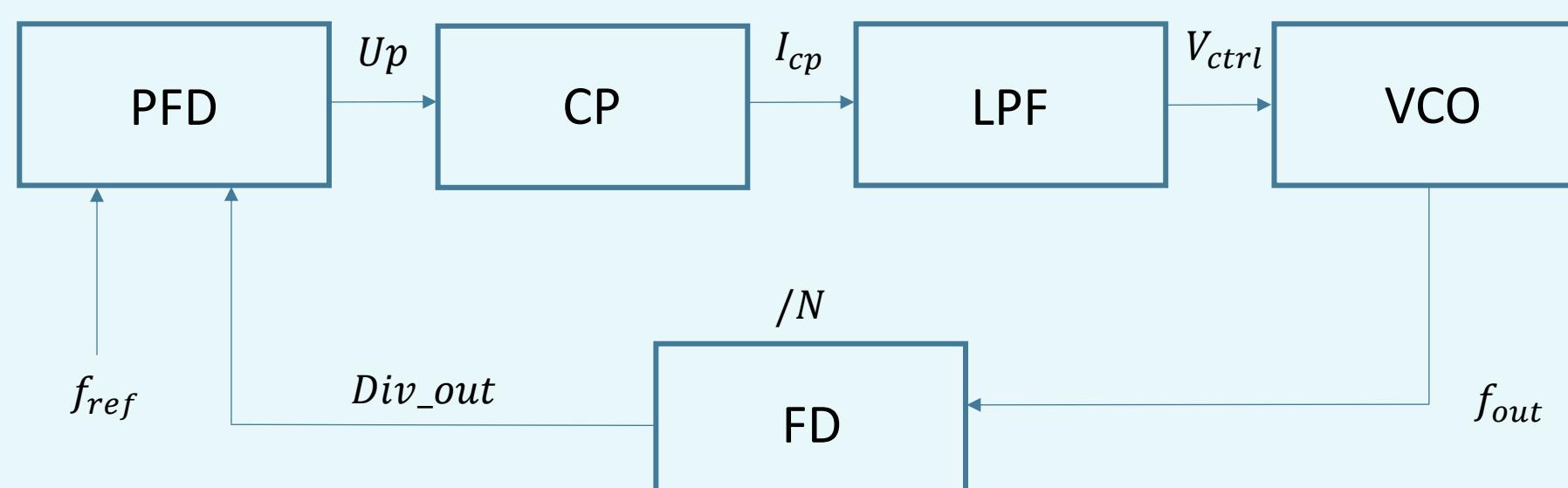

傳統鎖相迴路可以看作五個子電路的集合，其中包括相位頻率偵測器(Phase frequency detector, PFD)、充電泵(Charge pump)、迴路濾波器(Loop filter, LF)、電壓控制震盪器(Voltage-controlled oscillator, VCO)以及除頻器(Frequency divider, FD)。其工作原理可視為一個負回授系統，在負回授機制下，PLL 會持續調整輸出訊號的頻率，直到回授訊號和參考訊號在相位和頻率上達成一致，便完成鎖定。

## Phase Frequency Detector

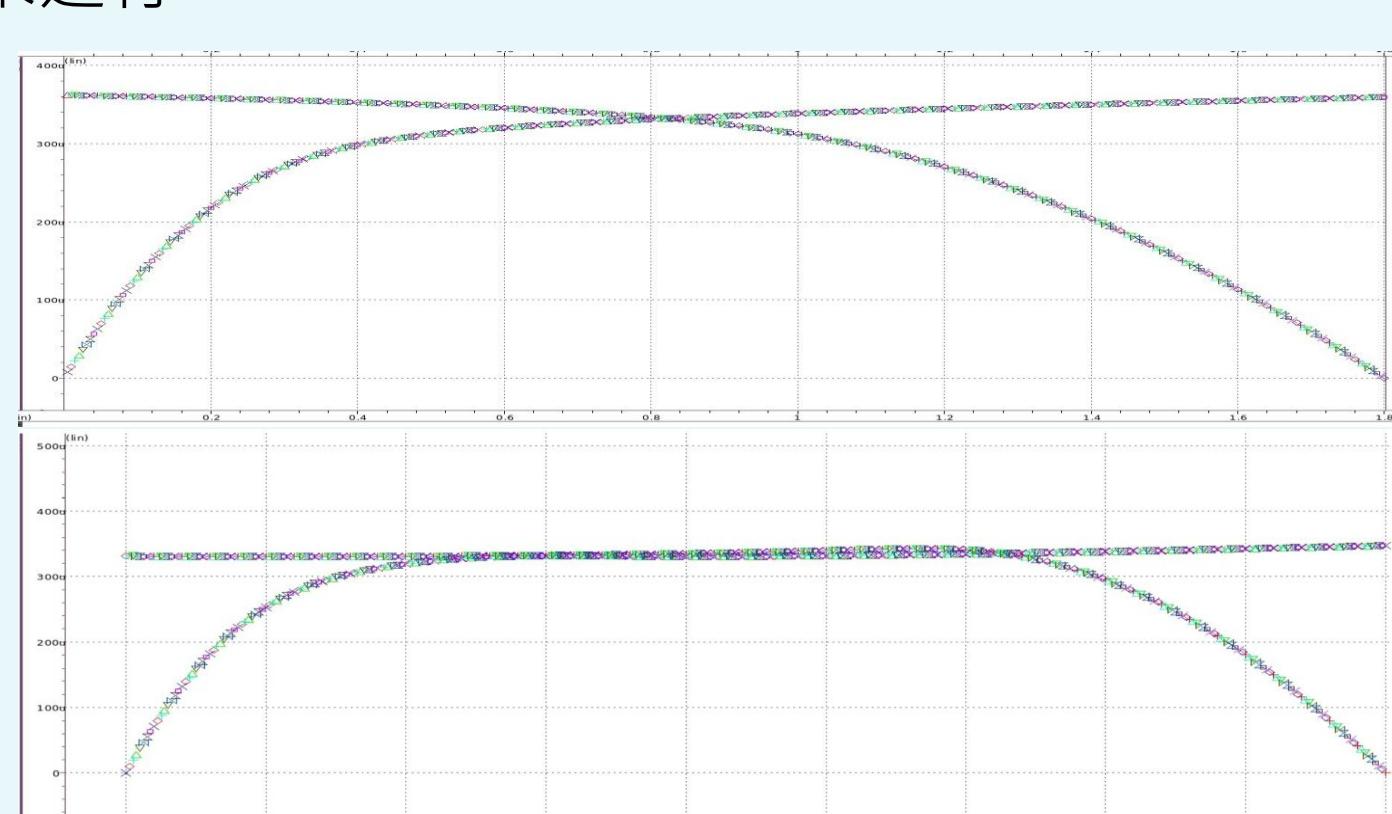

傳統PFD回授式重置路徑 (feedback reset path) 存在固有傳播延遲，其限制了電路的最大操作頻率，以及Dead Zone的產生，本次使用預先充電型PFD (Pre-charged PFD) 架構，架構移除了回授重置路徑，減少了死區的範圍，故PFD能夠偵測微小的相位差，以確保鎖相迴路達成高準確度且穩定的鎖定狀態。

## 實驗結果

| Process Tech                        | TSMC 0.18 $\mu\text{m}$ |

|-------------------------------------|-------------------------|

| Output frequency (GHz)              | 1.8                     |

| Power (mW)                          | 120                     |

| Core area ( $\mu\text{m}^2$ )       | 578 x 751               |

| Core $V_{DD}$ (V)                   | 1.8                     |

| Typical Lock Time ( $\mu\text{s}$ ) | 5                       |

| 電壓    | 溫度    | TT                | FF                | SS                |

|-------|-------|-------------------|-------------------|-------------------|

| 1.62V | -55°C | 5.6 $\mu\text{s}$ | 4 $\mu\text{s}$   | 6.8 $\mu\text{s}$ |

|       | 25°C  | 5.6 $\mu\text{s}$ | 4.5 $\mu\text{s}$ | 失敗                |

|       | 125°C | 5.6 $\mu\text{s}$ | 4 $\mu\text{s}$   | 失敗                |

| 1.8V  | -55°C | 5 $\mu\text{s}$   | 4 $\mu\text{s}$   | 6.9 $\mu\text{s}$ |

|       | 25°C  | 5 $\mu\text{s}$   | 4.3 $\mu\text{s}$ | 6.1 $\mu\text{s}$ |

|       | 125°C | 5 $\mu\text{s}$   | 3.6 $\mu\text{s}$ | 失敗                |

| 1.98V | -55°C | 3 $\mu\text{s}$   | 3.6 $\mu\text{s}$ | 失敗                |

|       | 25°C  | 4 $\mu\text{s}$   | 3.8 $\mu\text{s}$ | 4.2 $\mu\text{s}$ |

|       | 125°C | 4.8 $\mu\text{s}$ | 3.6 $\mu\text{s}$ | 4.3 $\mu\text{s}$ |

## 結論

在PVT變異條件下，系統於部分Corner仍出現鎖定失敗的情況，顯示穩定性尚有改善空間。此外本次設計中充電泵電流達 340  $\mu\text{A}$ ，使得系統整體功耗偏高，也是後續需要改善的部分之一。針對部分Corner無法鎖定的問題，希望透過數位校正和自適應偏壓技術來對電路進行改善，進一步提升電路在不同製程與環境條件下的穩定性，同時降低整體功耗，實現更具實用性和可靠的PLL系統。